# An Overview of the Asynchronous Digital Systems – Part 3

Assist.Prof. Grigore Mihai TIMIS, Ph.D., Dipl.Eng.

"Gh.Asachi" Technical University of Iasi,

Automatic Control and Computer Science&Engineering Faculty

Computer Science and Engineering department

mtimis@cs.tuiasi.ro

**Abstract**: Implementation methods for the digital asynchronous systems use different predefined models like self timed circuits, speed independent circuits, delay insensitive circuits, handshake protocol implementation in asynchronous systems, C Muller circuits.

**Keywords**: Asynchronous digital systems, self timed, speed independent, delay insensitive, handshake, C Muller.

#### 1. Introduction

In this paper, the author presents an overview of the asynchronous digital systems like self timed, speed independent, delay insensitive, handshake protocol implementation in digital asynchronous systems, C Muller circuits.

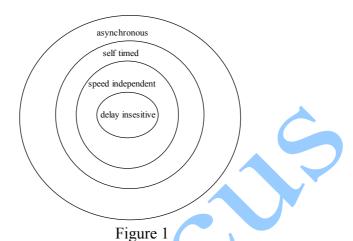

A delay insensitive circuit works correctly indifferent of the propagation timing delays through wires and circuits. This concept was firstly introduced by Clark and Molnar, [Cla67].

A speed independent circuit works correctly indifferent of the propagation timing delays through circuits. The wires have a specific delay propagation values. This concept was firstly in introduced by David Muller [Mul65].

A self timed circuit uses a temporized elements where the wires delay propagation timing are known or neglijable. Using the time information values, they are built like speed independent circuits, [MC80].

The asynchronous sequential systems represents the general category, [Ung69], they haven't a localy clock signal, they are running using internally timing values. The latches and flip-flops circuits works asynchronous, [Clu86], they have the time set-up and time-hold predefined values.

## 2. Delay insensitive circuits. C Muller circuits

A delay insensitive circuit has arbitrary delays for wires or logic gates. A delay insensitive circuit has macromodule blocks and the interconnection between them. Every macromodule block must be designed do not influence the stability of the entire digital system. The hardware logic design can be much harder to do because of the acknowledge ACK signal, [Huf54], [JJ96].

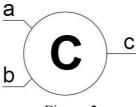

In this case is much better to use the Muller C logic gate, figure 2.

Figure 2

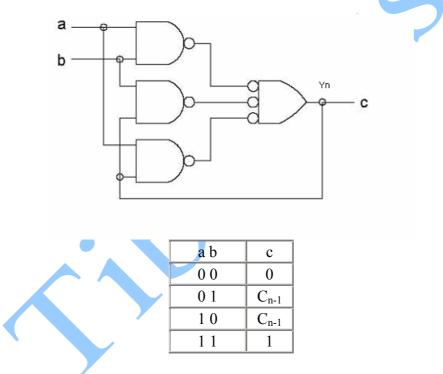

The internal C Muller logic gate design and the truth table are described in figure 3.

Figure 3

The equation for the C Muller logic gate is  $c = \overline{a} \cdot b \cdot c_{n-1} + a \cdot \overline{b} \cdot c_{n-1} + a \cdot b$ If used the notation c=yn+1, the C Muller logic gate equation is  $y_{n+1} = \overline{a} \cdot b \cdot y_n + a \cdot \overline{b} \cdot y_n + a \cdot b$ , the truth table is in figure 4.

| a b y <sub>n</sub> | $y_{n+1}$      |

|--------------------|----------------|

| 0 0 -              | 0              |

| 01-                | y <sub>n</sub> |

| 10-                | y <sub>n</sub> |

| 11-                | 1              |

Figure 4

When (abyn =00-) and (abyn=11-) it's done the write operation and when (abyn=01-) şi (abyn=10-) it'sdone the hold operation. The C Muller logic gate represents a logic latch circuit.

The delay in sensitive circuits are used as control circuits. A different delay model is represented by the speed independent circuits. It counts only the delays through logic gates, the wire delays aren't taken into account. A speed independent circuit runs good indifferent by the delays through logic gates.

The bounded delay means that the delay for every logic gate must be less than a maximum setted value. This model is common used in digital asynchronous systems.

A self timed circuit instantaneous calculates the value for a logic gate and after a delay it assigns it to the output, [Dil89].

### 3. Data valid protocol

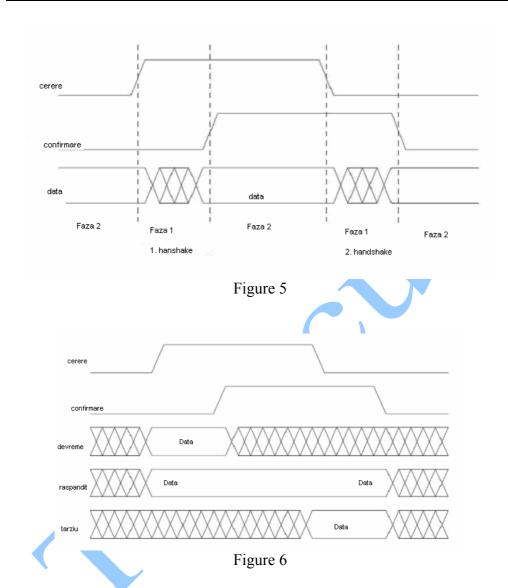

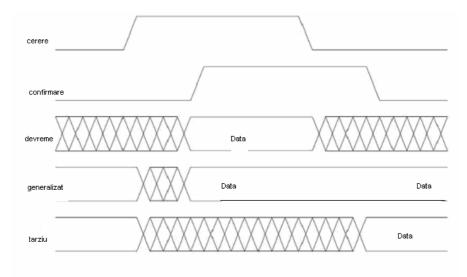

In the asynchronous communication systems a wide range of protocols exists, figure 5, 6.

In the broad protocol, the data must be valid during the handshake protocol. In the late protocol, data must be valid between the negative transitions on the request, acknowledge signals.

The four phase pull chanell with aditional protocols for the datas are ilustrated in figure 7.

Figure 7

In this case, the receiver is the active part which request datas from the sender. For the early protocol, datas must be valid between the positive signals from the sender and the negative signals from the receiver.

For the broad and late protocols, data must be valid between hanshake processes.

#### **Conclusions**

Using the predefined circuit models in implementation of asynchronous digital systems means avoid errors and digital hazard situations. The digital asynchronous system will run correctly, according with the specifications.

### 5. References

[Cla67] W. A. Clark, *Macromodular computer systems*, In Proceedings of the Spring Joint Computer Conference, AFIPS, April 1967

- [Clu86] E. J. McCluskey, Logic Design Principles: with emphasis on testable semicustom circuits, Prentice Hall, Englewood Cliffs, NJ, 1986

- [Dil89] D. L. Dill, Trace Theory for Automatic Hierarchical Verification of Speed Independent Circuits, MIT Press, Cambridge, MA, 1989.

- [Huf54] D. A. Huffman, *The Synthesis of Sequential Switching Circuits*, J. Franklin Institute, March / April 1954

- [JJ96] G. Jennings, E. Jennings, A Discrete Syntax for Level Sensitive Latched Circuits Having n Clock and m Phases, In IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, col.15, No.1, January 1996, pp.111-126

- [Mul65] R. E. Muller, Switching Theory. Volume II: Sequential Circuits and Machines, John Wiley and Sons, New York, NY, 1965.

- [MC80] C. Mead, L. Conway, *Introduction to VLSI Systems*, Addison Wesley, Reading, MA, 1980, C.L.Setiz, System Timing

- [Ung69] S. H. Unger, Asynchronous Sequential Switching Circuits. Wiley Interscience, New York, NY, 1969